**Georgia** Institute for Electronics **Tech** ∄and Nanotechnology

## Welcome

# Industry

## **Students**

## Staff

# Faculty

Key

- 1. Industry Members 51

- 2. Students and PRC staff 54

- 3. Faculty and research staff 17

- 4. Non Members 18

**Total: 140 Attendees**

### **Outline**

Georgia Tech

PACKAGING

RESEARCH

CENTER

- ☐ PRC Overview

- Organization

- Membership & Benefits

- System Scaling enabled by Heterogeneous Integration

- Research Areas

- ☐ IAB Meeting Format

### **PRC Team**

- Several Federally Funded Research Programs

- Mega-center on packaging & system scaling with expertise in Chip – Package – System

- Positioning: #1 Academic Center on Packaging around the Globe

### **PRC Students**

### **Collaborators**

**SYNOPSYS®**

TOKYO OHKA KOGYO CO., LTD.

### **Shared User PRC Facilities**

- ☐ Comprehensive global Industry Consortium in System Scaling to enable supply-chain manufacturing to end-user needs

- ☐ Industry culture and R&D infrastructure (300mm clean room facility)

**Plating Facility**

Substrate Cleanroom

**Assembly Facility**

**Environmental Testing**

Shared User Labs

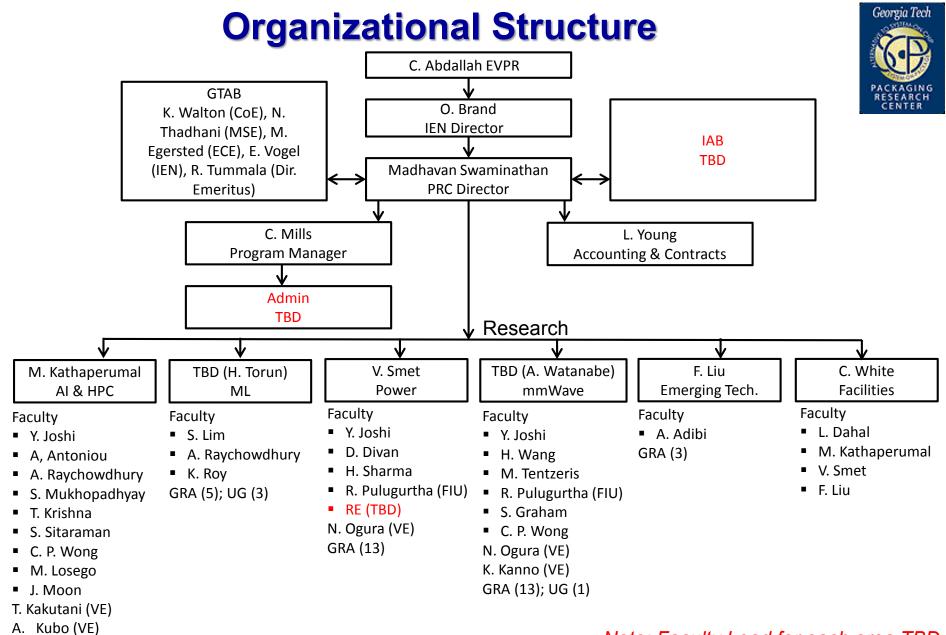

Note: Faculty Lead for each area TBD

GRA (10); UG (1)

### **System Scaling**

Scaling

Size Performance

Functionality

Georgia Tech

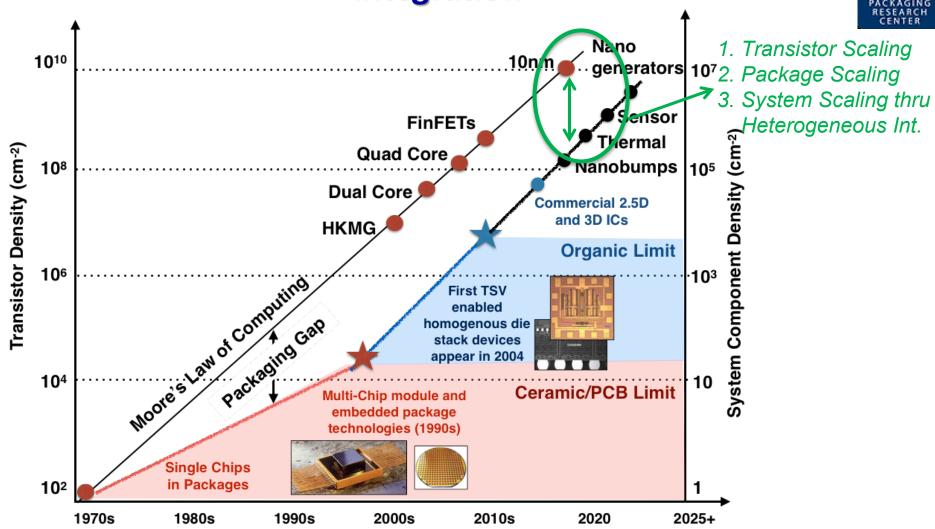

# Vision – System Scaling through Heterogeneous Integration

M. Swaminathan and K. Han, "Design and Modeling for 3D ICs and Interposers", WSPC 2013 Modified: Arijit Raychowdhury, GT

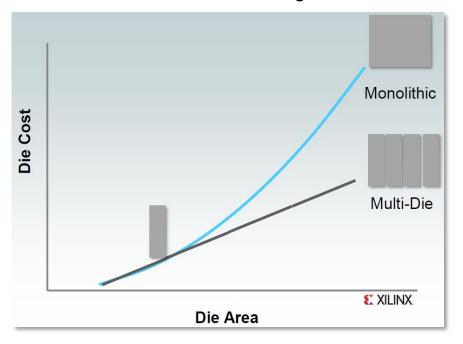

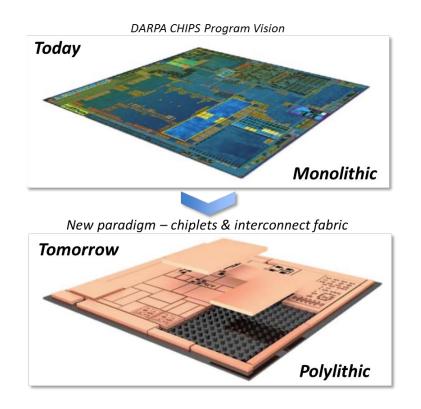

### From Monolithic to Polylithic (Heterogeneous) Integration

Cost of Monolithic Integration

### Shift to <u>packaging</u> as most cost-effective path to further system scaling

Georgia Tech

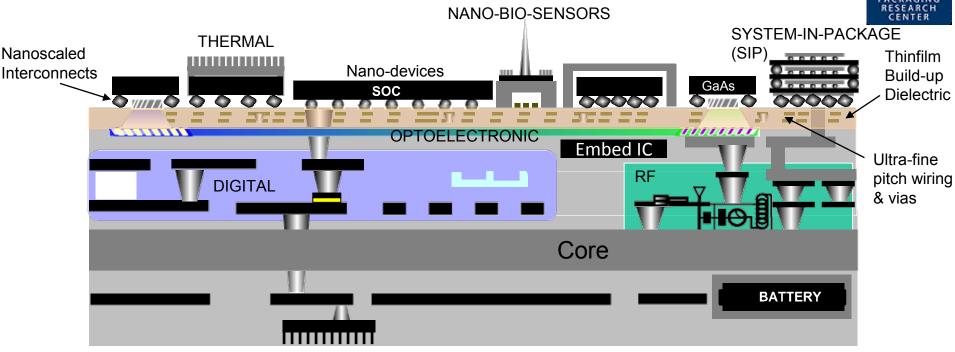

# System on Package (SOP) Heterogeneous Integration Platform

ULTRA HIGH DENSITY I/O INTERFACE

- □ Advanced Devices

- ☐ 3D Memory, Spintronic Logic/Memory, Ultra WB, Compute Logic

- ☐ Assembled onto an Integrated Package with functional layers @ fine pitch

- ☐ RF, Optical, Inductors, Capacitors, Sensors, Battery, Thermal

- ☐ Leading to scaled systems

Georgia Tech

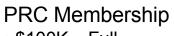

### **PRC Membership & Benefits**

- \$100K Full

- \$65K Student

- \$25K Supply Chain

Large Multi-year Programs

GT Proprietary Information to Center or Program Members:

- NERF IP Licenses

- Advanced Access

- Project Mentorship

- Supply Chain Engagement

- Targeted Student Access

Knowhow and Information published in public domain:

- New Technical Info

- More Student Access

- Expanded Faculty Expertise

- Available without added \$

sign Methods, Machine Learning, Tools

Semiconductors.

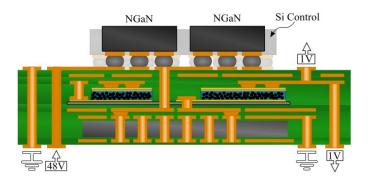

**Power Delivery Networks and Devices**

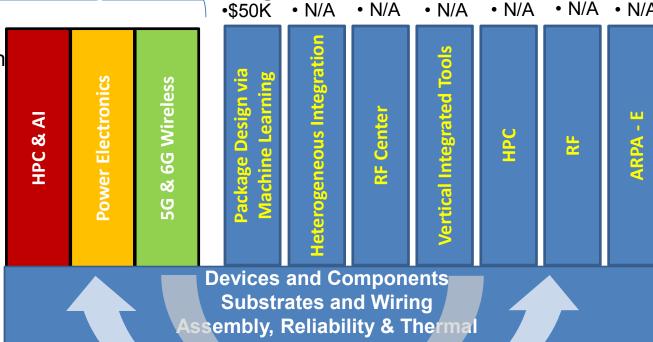

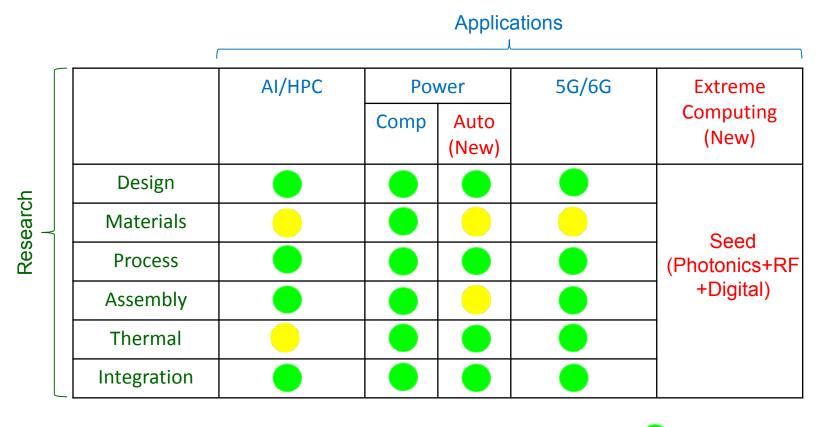

### **Research & Application Matrix**

- ☐ Matrix used to engage Industry & Faculty

- ☐ Helps identify investment and expansion areas

Well Covered

Partially Covered

Not Covered

### PhD Proposals (2019)

Shreya Dwarakanath. RDL, June '19 (joining Intel)

Tong-Hong Lin, RF, May 119

Kashyap Moh?

Rui Zhang, Optoelectron ics, Oct '19

Bart DeProspo, RDL, D€

Hakki Torun, Machine Learning,

Tailong Shi, RF, Dec '19

Haksun Lee, Automotive, Oct '19

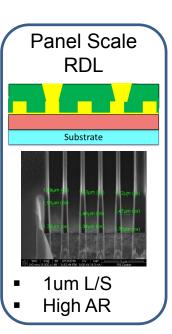

### **PhD Graduations**

Dr. Chandrasekhar S. Nair

Modeling, Design, Materials,

Processes and Reliability of

Multi-Layer Redistribution

Wiring Layers on Glass

Substrates for Next

Generation of HighPerformance Computing

Applications, May 2019

Employer: Intel Corp.

Dr. Huan Yu

Behavioral Modeling of

Drivers and Oscillators

using Machine

Learning, Oct. 2019

Employer: Apple

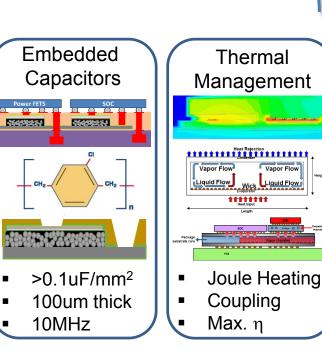

Dr. Robert G. Spurney

Advanced Materials

and Processes for

High-Density

Capacitors in NextGeneration Integrated

Voltage Regulators,

Aug 2019

Employer: TI

### **Student Summer Internships**

Georgia Tech

PACKAGING

RESEARCH

CENTER

- 1. Huan Yu: Apple, 2019

- 2. Hakki Torun: Intel, 2019

- 3. Nithin Nedumthakady: Intel, 2019

- 4. Kashyap Mohan: TI, 2019

- 5. Atom Watanabe: Qualcomm, 2019

- 6. Muhammad Ali: Apple, 2019

Several students looking for <u>Internship</u> during Summer 2020. Please interact with students during poster session!

### **Neuromorphic Computing**

Adapted from "The future of electronics based on memristivesystems" Mohammed A. Zidan, John Paul Strachan & Wei D. Lu, Nature Electronics 2018

Courtesy: Yole Development

- ☐ Future of Computing

- ☐ GPU+CPU+CMOS limited by Moore's Law, Memory Wall & Heat Wall

- ☐ Move towards Neuromorphic sensing/computing with better memory access

- ☐ Large emerging market in Automotive, Industrial & Consumer segments over next decade

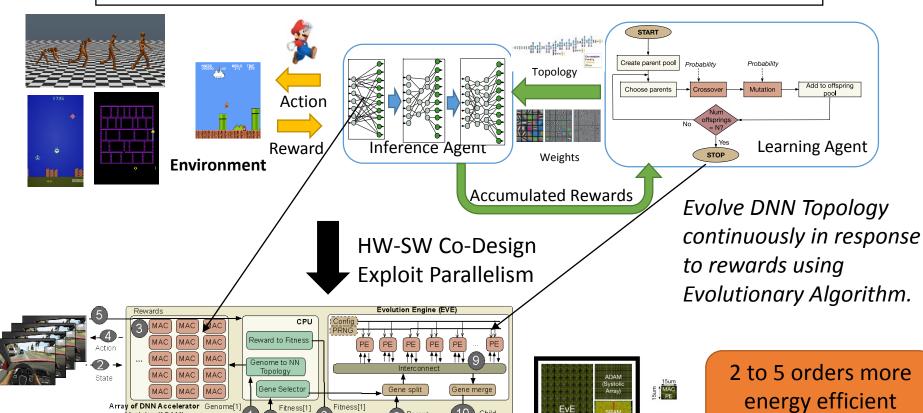

# GeneSys: Enabling Continuous Learning using Neuro-evolution in Hardware

How do we learn at the edge in the <u>absence</u> of a (i) trained DNN model (ii) labeled data sets or (iii) connectivity to a backend cloud server

Ananda Samajdar, Parth Mannan, Kartikay Garg, and <u>Tushar Krishna</u>,

Fitness 1

GeneSys: Enabling Continuous Learning through Neural Network Evolution in Hardware, MICRO 2018

Genome Buffer

than CPUs and GPUs

### **System Architecture – Digital/Wireless Convergence**

Georgia Tech

### **AI & High Performance Computing**

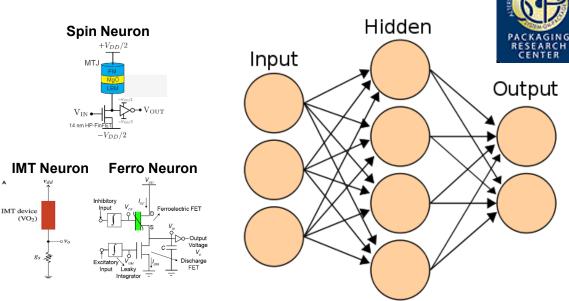

Courtesy: ASCENT, JUMP

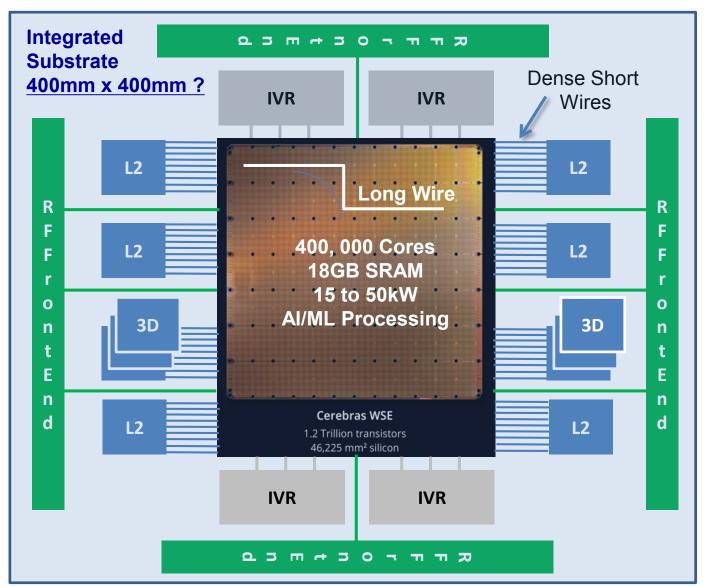

- ☐ Limited by memory bandwidth where read/writes are performed at course granularities

- ☐ Massively parallel architecture supported by dense connectivity

- ☐ Suitable for life long learning and decision making in changing environment

- ☐ Co-located logic and memory (In Memory & Near Memory)

- ☐ Vertical CMOS & Beyond CMOS device technologies

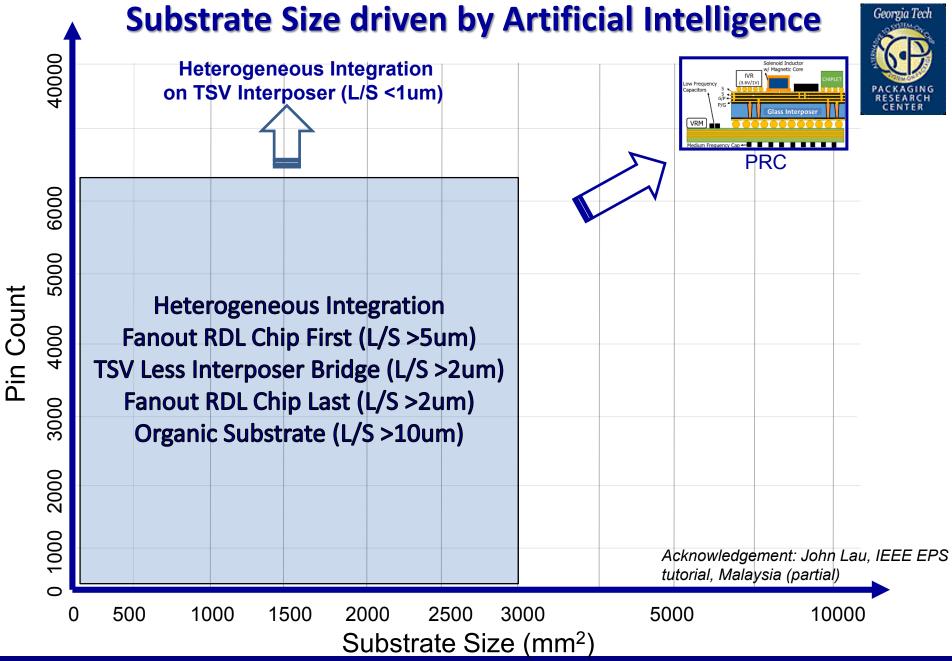

- ☐ Heterogeneous Integration with large substrate sizes (A better approach)

### **Al & High Performance Computing**

**Research Focus Areas**

#### **Research Focus Areas**

Georgia Tech

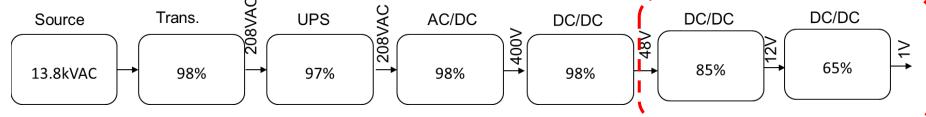

### **Data Centers & Energy**

- Data Centers consume 70 billion KWh today in USA

- ☐ For every 2W drawn from the grid only 1W is used by the Data Center

- 20% improvement in efficiency can translate to 20% reduction in energy consumption

Source: Dept. of Energy, USA

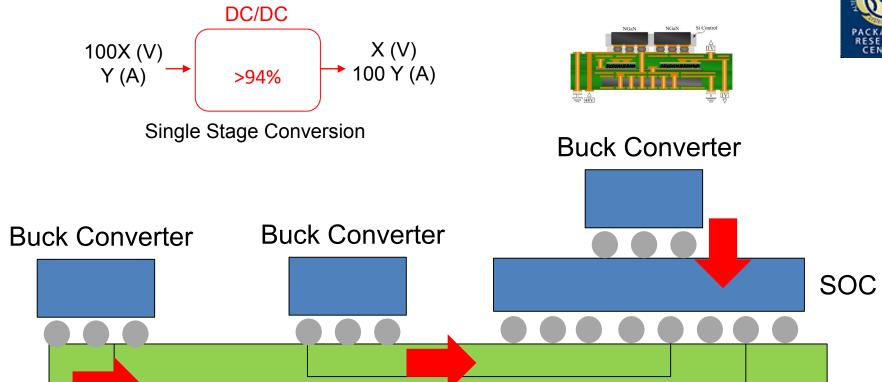

### **Efficient Power Delivery in Microsystems**

- ☐ Bring the converter (power source) in close proximity to SOC

- Significantly reduce Cu losses due to shorter current paths

- □ Need: High Efficiency, Highly Integrated, Highly Miniaturized, High Conversion Ratio, Single Stage Converters

- Low energy circuits

### **Power Electronics - Computing**

**Research Focus Areas**

**Research Focus Areas**

L&C

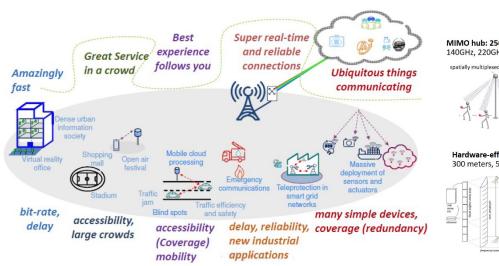

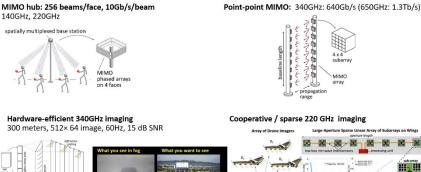

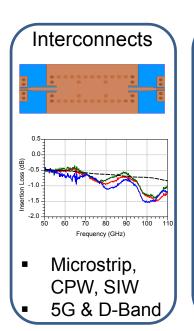

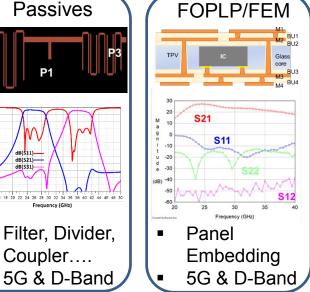

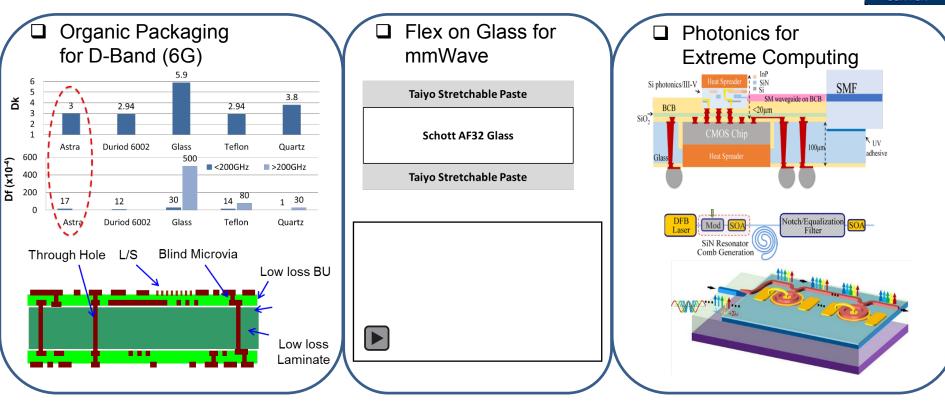

### 5G & 6G Wireless

5G 6G

Courtesy: M. A. M. Albreem, I4CT '15

Courtesy: ComSenTer, JUMP

- 5G mmWave 24GHz 86GHz

- High levels of attenuation

- Increase the data bandwidth available over smaller, densely populated areas

- increase data capacity, decrease latency and connect many more devices

- 6G sub-THz (0.1 0.5 THz)

- MIMO, Imaging, Non-destructive testing, Virtual Reality ....

- Requires new materials & package integration technologies

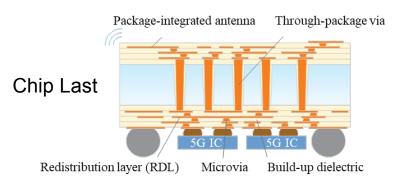

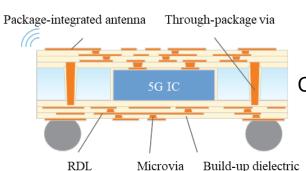

### **5G & 6G Wireless**

Chip First

#### **Research Focus Areas**

#### **Research Focus Areas**

# **Antennas** High Gain & BW 5G & D-Band

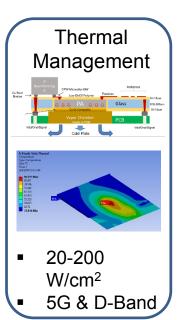

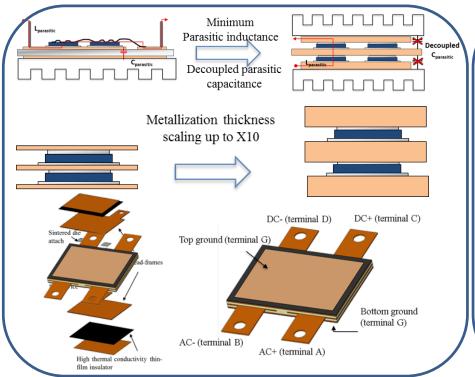

### Power Electronics – Automotive (New)

B. K. Chakravarthy and G. Sree Lakshmi, "Power Savings with all SiC Inverter in Electric Traction applications," *E3S Web Conf.*, vol. 87, pp. 1-14, 2019.

- Move towards SiC based modules

- Need for <u>3D Integrated Packaging</u> that reduces parasitics & improves thermal performance

- Exploration of <u>new package architectures</u> required!

Georgia Tech

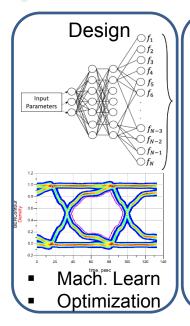

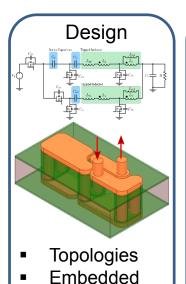

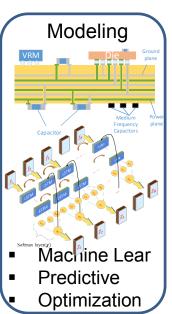

### 3D Integrated Packaging & Machine Learning

Generate new power module **Bayesian Active** Device \_\_ Circuit Power Converter Technology Topology Learning →3D → Interconnect → Cooling → Material and Geometry Packaging Architecture Performance Metrics: Electrical dV/dt, power density, Multi-Physics Simulation efficiency, thermal Mechanical Thermal < stability, volume, cost

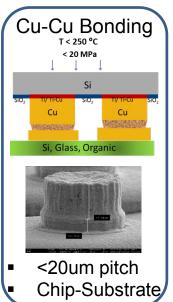

- 3D Integrated Packaging for:

- High speed switching

- High thermal capacitance

- Double-sided large area interconnect

- Minimized thermal gradient within the package

- Highly modular solution for manufacturing

- ☐ Use of Machine Learning to:

- Develop new package architectures

- Optimize structures to minimize design cycle time

- Remove human out of the loop

- Investigate new materials and interfaces

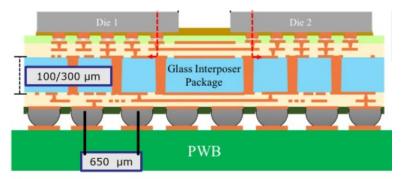

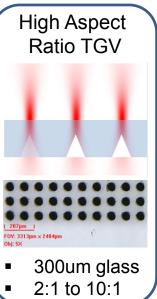

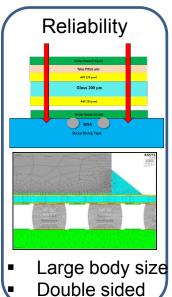

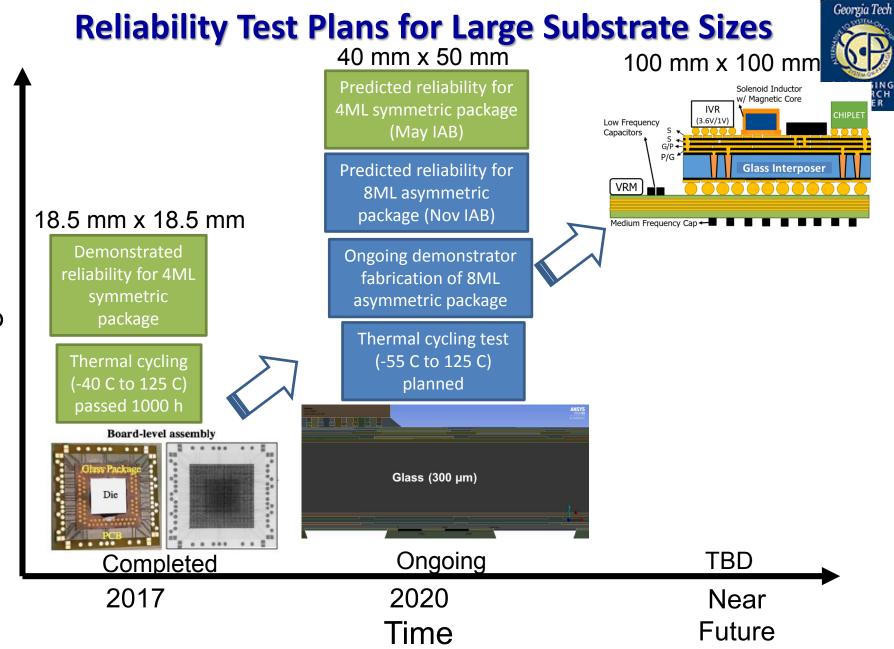

### Thin Glass as a Substrate Material

### **Emerging Technologies (New)**

- □ Session IV

- Based on industry feedback from May '19 IAB

- Industry please provide feedback on your interest level in these areas

### **IAB Meeting Format**

- Four Sessions

- Session I: AI & HPC

- Session II: Power Electronics

- Session III: 5G & 6G

- Session IV: Emerging Technologies

- ☐ Sessions I, II & III

- Oral Presentations

- One Slide Poster Introduction

- Poster Session

- Session IV (Oral Presentation only)

- ☐ Industry feedback after each session

- ☐ PRC Membership Details on Nov 8 (AM)

### Thank you