# Advanced Panel RDL Technologies for High Performance Computing (HPC) Applications

#### **Faculty:**

Dr. Mohan Kathaperumal

Dr. Fuhan Liu

Prof. Tummala

Prof. Swaminathan

**Students:** Bartlet DeProspo, Siddharth Ravichandran, Pratik Nimbalkar, Shreya Dwarakanath, Rui Zhang, Omkar Gupte, Hakki Torun

### **Outline**

- ☐ Goals & Objectives

- ☐ Prior Work

- □ Technical Approach

- ☐ Results & Key Accomplishments

- ☐ Comparison with Prior Art

- ☐ Schedule

- □ Summary

# Goals and Objectives

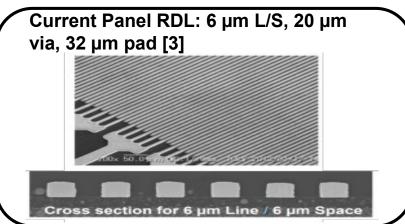

|                           | Parameters                                                                                                                                     | Si BEOL RDL                                                                                                                       | Current Panel RDL                                                                                                                     | Proposed RDL                                                                                                               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Modeling                  | Aspect Ratio                                                                                                                                   | • 1-2                                                                                                                             | • 1-2                                                                                                                                 | >4                                                                                                                         |

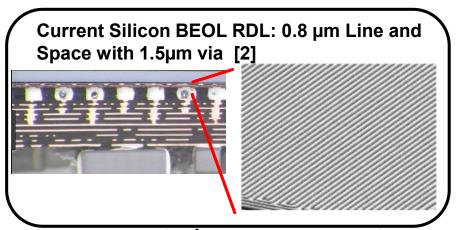

|                           | Conductor     Width/Spacing                                                                                                                    | 0.8/0.8 μm                                                                                                                        | 6/6 µm                                                                                                                                | 1/1 µm                                                                                                                     |

| Design                    | • Single-Ended Impedance ( $Z_o$ in $\Omega$ )                                                                                                 | • 47                                                                                                                              | • 55                                                                                                                                  | • 50                                                                                                                       |

|                           | Data Rate Per<br>Channel (Gbps)                                                                                                                | • 2                                                                                                                               | • 2-5                                                                                                                                 | >10                                                                                                                        |

| Materials • (Photoresist) | <ul> <li>Thickness</li> <li>Chemical     Composition</li> <li>Exposure Mechanism</li> <li>Type</li> <li>Substrate     Compatibility</li> </ul> | <ul> <li>Ultra-thin &lt;1 µm</li> <li>Chemically     Amplified</li> <li>Polarization</li> <li>Liquid PR</li> <li>Wafer</li> </ul> | <ul> <li>Thick &gt;10 µm</li> <li>Non-Chemically<br/>Amplified</li> <li>Polymerization</li> <li>Dry Film PR</li> <li>Panel</li> </ul> | <ul> <li>Thin &lt; 7 µm</li> <li>Chemically-Amplified</li> <li>Polarization</li> <li>Dry-film PR</li> <li>Panel</li> </ul> |

| Tools (Lithography)       | • NA<br>• DOF                                                                                                                                  | <ul><li>&gt;0.28</li><li>±1.88 μm</li></ul>                                                                                       | • <0.13<br>• ±10 µm                                                                                                                   | <ul><li>0.18 – 0.24</li><li>±4.2 μm</li></ul>                                                                              |

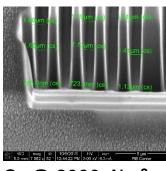

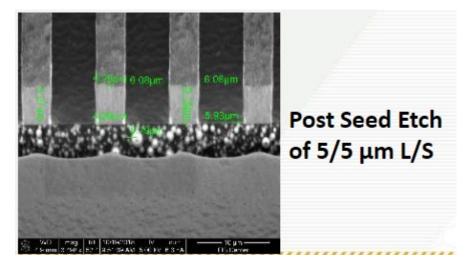

| Processes                 | <ul><li>RDL Formation</li><li>Metallization</li></ul>                                                                                          | <ul><li>Dual Damascene</li><li>PVD Seed</li></ul>                                                                                 | <ul><li>SAP</li><li>Electroless Seed</li></ul>                                                                                        | <ul><li>Advanced SAP</li><li>PVD Seed</li></ul>                                                                            |

### **Prior Work**

- Explored the difference between Liquid and Dry films specifically around performance on rough dielectric surfaces

- Demonstrated planarized multi-layer SAP with 4 μm diameter microvias

- Demonstrated 2 μm microvias in no filler dielectrics and nano-sized filler dielectrics

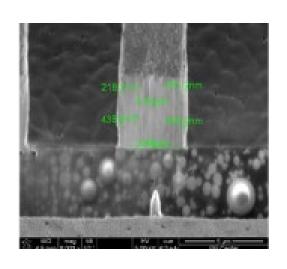

- ☐ Worked with AMAT to develop a new highly selective wet chemistry for seed layer etch

### **Technical Approach**

#### **Materials**

- ➤ Ultra-Thin, Low D<sub>k</sub> Dielectrics

- Panel Processable

- Low CTE, Low Modulus, High Elongation to Break

#### **Processes**

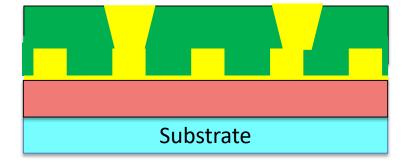

- Panel-Scale Semi-Additive Process

- Surface Planarization for High Yield RDL formation

- End Point Seed Etch Detection

#### **Interconnects**

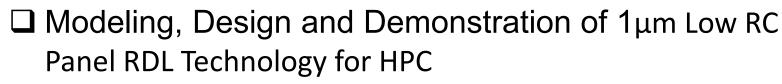

Low R, Low C 2 um Multi-Layer RDL with 50 ohms impedance matching

#### Low Cost

- Low Cost, Panel Scale Processes

- > Large Body Size Substrates

#### **Assembly**

- Chip-level interconnect

- TCB Cu pillar

- Board-level interconnect

- Large body 30 mm x 40 mm SMT

#### **Thermal**

Advanced Direct Cu plated heat sinks

#### Reliability

- RDL Reliability

- Fine pitch traces and u-vias

- Multi-Layer RDL Reliability on Glass

- > Interconnect

- Chip Level interconnects at 35 um pitch

- Board Level with 7 ppm/K CTE Glass core

# Results & Key Accomplishments

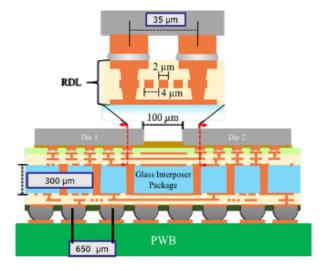

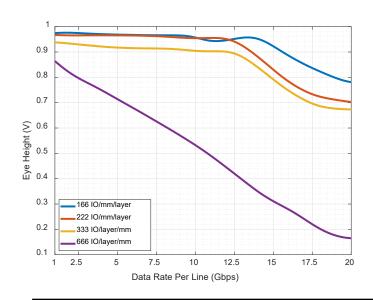

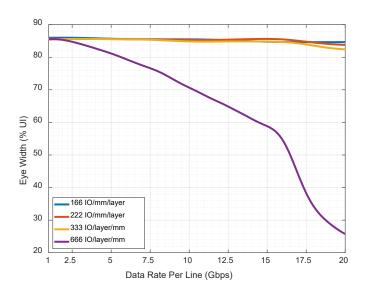

Optimal I/O Density Design Rules for Maximum Data Rate per Channel – Hakki Torun

| IO Density      | Optimal Width/Spacing/Aspect Ratio | Max Data Rate<br>per Line | Achievable<br>Aggregated Bandwidth |

|-----------------|------------------------------------|---------------------------|------------------------------------|

| 166 IO/mm/layer | $1\mu m/10\mu m/1.2$               | 18.9 Gbps                 | 3.14 Tbps/mm/layer                 |

| 222 IO/mm/layer | 0.5μm/8μm/3.6                      | 15.6 Gbps                 | 3.46 Tbps/mm/layer                 |

| 333 IO/mm/layer | $0.5\mu m/5\mu m/4.2$              | 14.8 Gbps                 | 4.93 Tbps/mm/layer                 |

| 666 IO/mm/layer | $0.5\mu m/2\mu m/3.0$              | 2.4 Gbps                  | 1.59 Tbps/mm/layer                 |

# Results: Seed Layer Reflectivity Study

Cu @ 1200 J/m<sup>2</sup>

Cr @ 1200 J/m<sup>2</sup>

Ag: 1200 J/m<sup>2</sup>

Ag @ 1600 J/m<sup>2</sup>

Cu @ 2000 J/m<sup>2</sup>

Cr @ 1600 J/m<sup>2</sup>

Cr @ 2000 J/m<sup>2</sup>

A @ 2000 J/m<sup>2</sup>

- Copper Reflects at 45%, Chromium at 23% and Silver reflects above 95% at 365 nm

- **Optimum dose** increases with a reduction in reflectivity

- **Optimum dose** decreases with an increase in reflectivity

## Results and Accomplishments: Provisional Patents

- Provisional Patent 1: SP SAP (Sidewall Protected SAP)

- Chandra Nair, Bart DeProspo, Omkar Gupte, Rao Tummala

- Wet chemical etching is extremely isotropic and attacks all portions of the RDL traces during seed layer removal. This disclosure is designed to induce an anisotropic aspect to this process for extending SAP to 1 µm and beyond.

- Provisional Patent 2:SAV SAP (Self-Aligned Via SAP)

- Bart DeProspo, Chandra Nair, Emanuel Surillo, Rao Tummala

- Electronics packaging utilizes laser technology to define the layer to layer via connections. The resolutions of these technologies is beginning to reach their limitations and taper angles are extremely high and require large pads for scaling. This disclosure's main benefit is around using a PR To scale via resolution and also to try and remove the large pad structures.

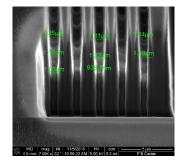

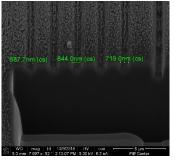

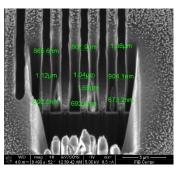

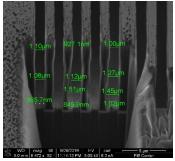

### Results: SP – SAP First Process Demonstration

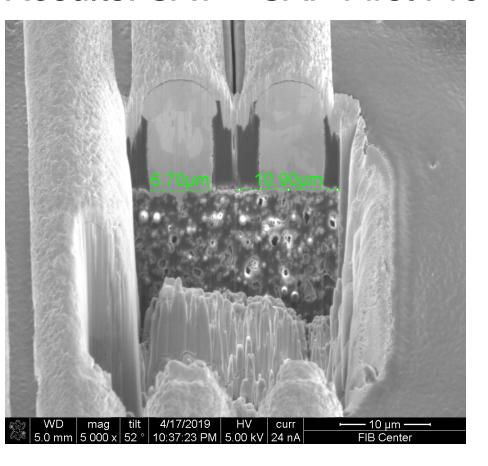

- Deposited 500 nm of parylene film onto the sidewall of copper traces using a CVD room temperature process

- The dielectric constant of parylene film is ~2.4 enabling low capacitance RDL

- As seen across the images there was no undercut of the trace during this process.

- Goal is to demonstrate this process in the future on line and space features that are ≤ 1μm CD working with partner companies.

### Results: SAV – SAP First Process Demonstration

Strip Photo-imageable material and deposit dielectric

- Goal for this work is to induce some misalignment at GT and test the limit of this process

- Design work suggests that highest performance system isn't necessarily matched in terms of line and space

Georgia Tech

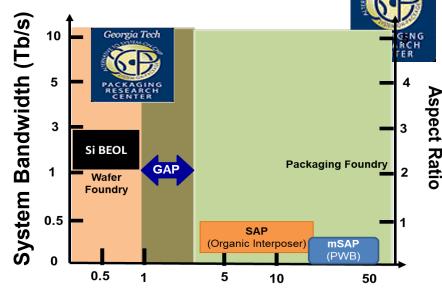

### Comparison to Prior Art Slide

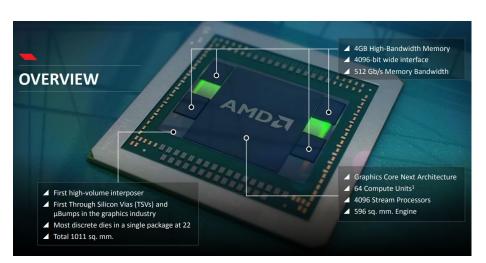

AMD Fiji GPU [1]

RDL Routing Line & Space, µm

Require High I/O Density RDL with Low Resistance capable of enabling High Bandwidth Systems on Panel RDL

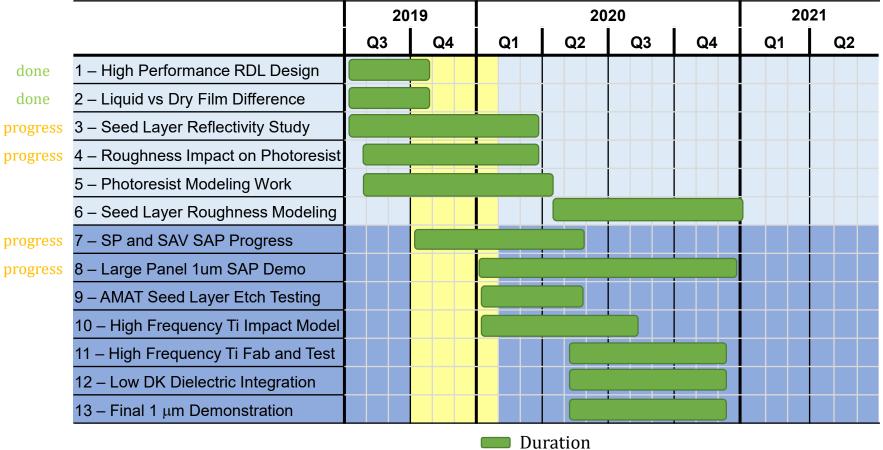

### Schedule

Georgia Tech

# Summary

- Completed Electrical Design work for high performance RDL design

- □ Courtesy of Hakki Torun

- ☐ Fabricated and analyzed impact of seed layer reflectivity on photoresist performance

- ☐ Filed provisional patent on new sidewall protected semi additive process