### Georgia Tech PACKAGING RESEARCH CENTER

# **SRC**<sup>®</sup> JUMP

# Inductor & Power-Stage Co-Design for 48V to 1V Integrated Voltage Regulators (HV-IVR)

**GT Team:** Claudio Alvarez Srinidhi Suresh Venkatesh Avula Dr. Himani Sharma Dr. Raj Pulugurtha

Advisor:Prof. Madhavan SwaminathanProf. Rao Tummala

The authors wish to acknowledge the funding support provided by the Georgia Tech PRC industry consortium members. This work was supported in part by ASCENT, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA.

## Outline

- 1. Motivation and Objectives

- 2. Figure of Merit (FoM)

- 3. Technical Approach

- Challenges

- Power Stage

- Inductor and Comparison to Prior-Art

- Co-Design Requirements

- 4. Results & Key Accomplishments

- Proposed Inductor Structure

- Fabrication Process

- 5. Summary and Schedule

### Motivation

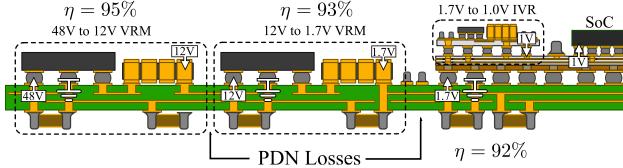

- Power Distribution Networks (PDN) in data centers and servers have multiple down-conversion stages from the AC grid to the SoC load.

- Many power loss sources in the PDN chain from 48V backplane to 1V System-on-Chip.

- System efficiencies can be as low as 70%

### Objective

3

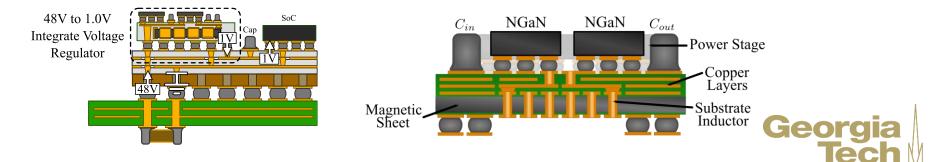

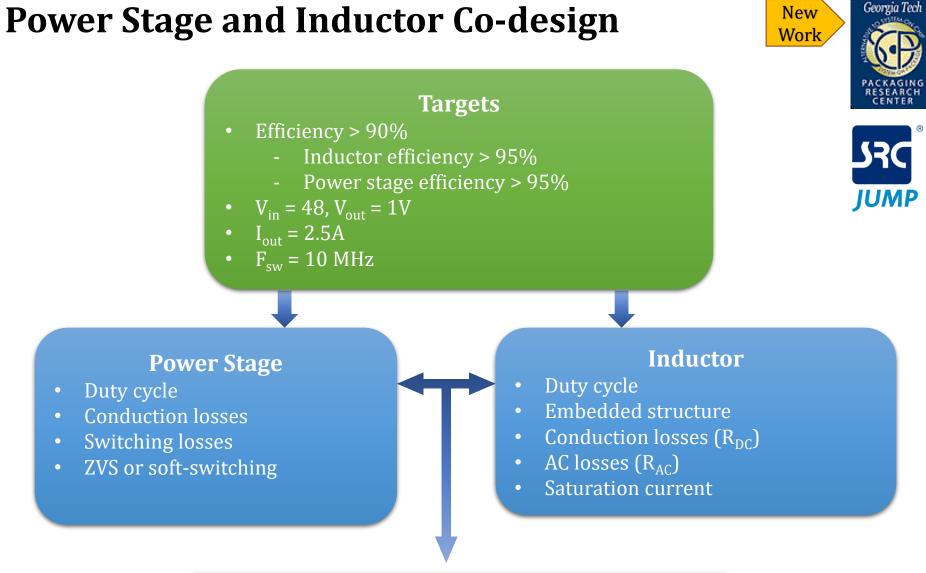

- Design and demonstrate a 48V to 1V IVR with GaN FETs and embedded inductors.

- Efficiency greater than 90% (Power stage: 95% and Inductor: 95%)

- 1V output voltage, 2.5A output current per phase

- 10 MHz switching frequency to allows passives components miniaturization

JUMP

### **PRC IAB Meeting**

### **Figure of Merit (FoM)**

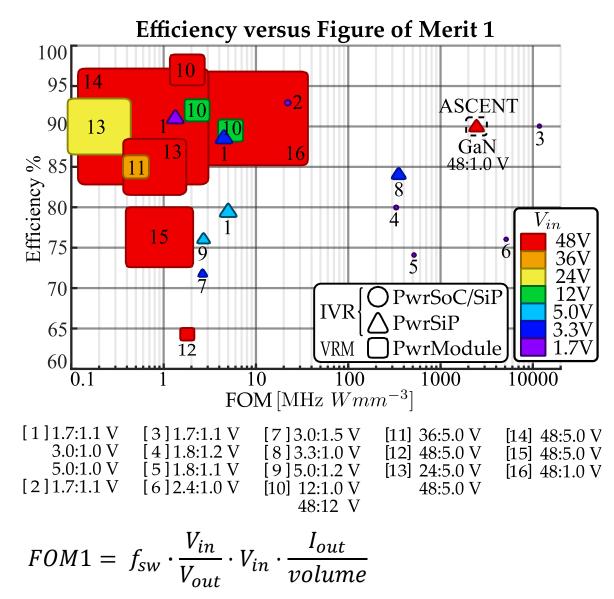

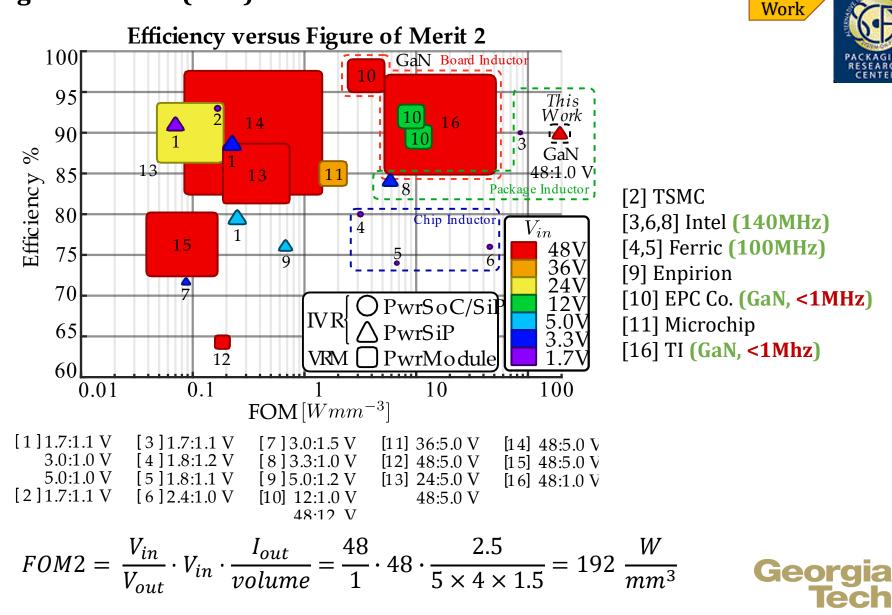

- The color represent the Input voltage.

- The shape represent the type of integration.

- And the size represent the relative solution volume.

- The frequency in the FOM makes it difficult (unfair) the comparison.

New

Georgia Tech

### **PRC IAB Meeting**

### Figure of Merit (FoM)

5

5

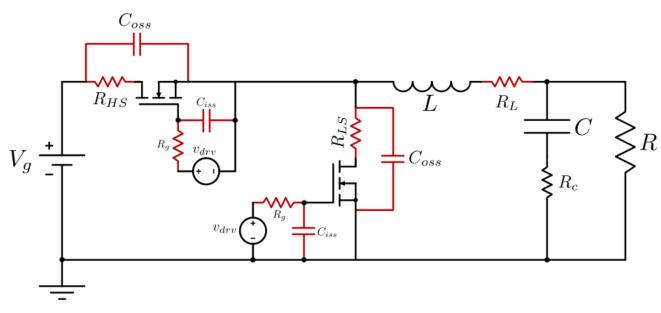

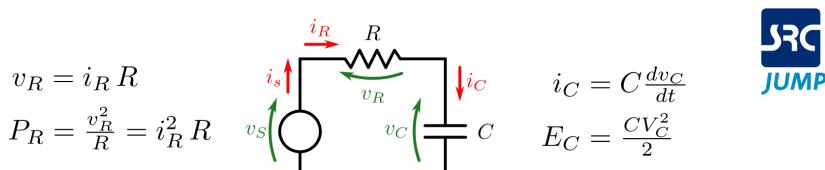

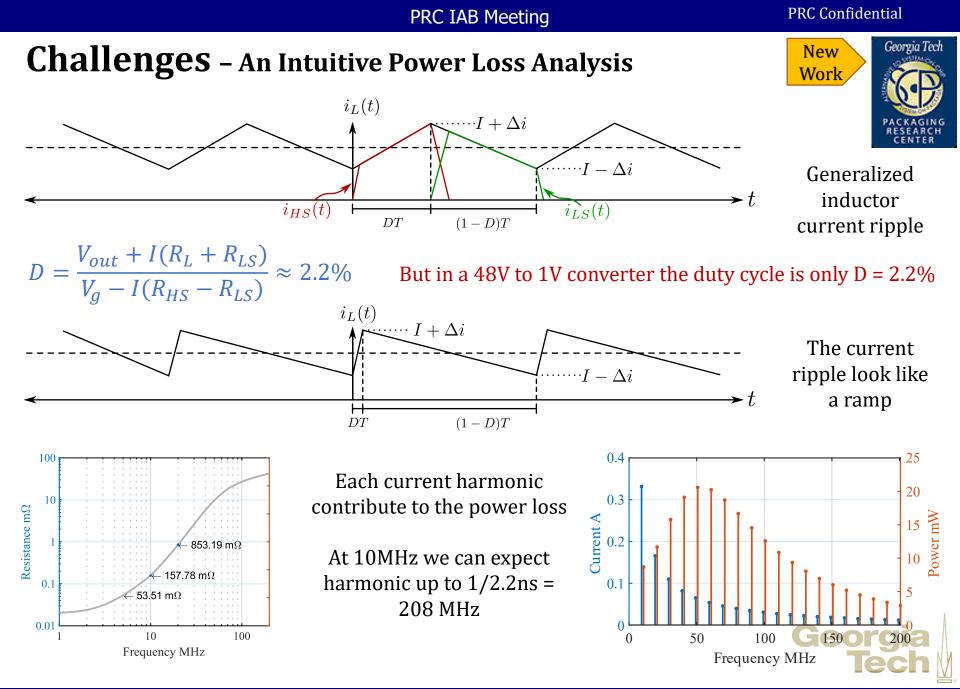

## **Challenges** – An Intuitive Power Loss Analysis

The simplest hard-switched buck converter Elements in red burn power, reducing the efficiency

November 7 and 8, 2019

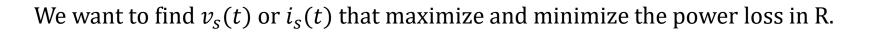

## **Challenges** – An Intuitive Power Loss Analysis

Let consider the simple RC network, where C is charge by a generic source.

$$\min(P_R) \implies i_S \equiv const. \implies P_R = I_{RMS(R)}^2 R$$

$$\max(P_R) \implies v_S \equiv const. \implies E_R = \frac{CV_C^2}{2}$$

7

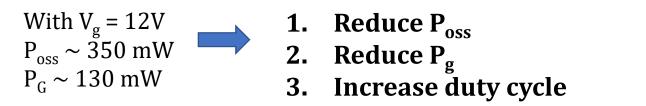

# **Challenges** – An Intuitive Power Loss Analysis

- Every time the HS switch is turn on,  $\frac{C_{oss}V_g^2}{2}$  energy is lost

- Every time a switch is turn on and off,  $\bar{C}_{iss}V_{drv}^2$  energy is lost

- Every switching period

- Duty cycle  $D = \frac{1}{48} = 0.021$  means at 10 MHz an on-time of 2.1ns.

- State of the Art GaN driver has minimum on-time between 5ns to 10ns.

November 7 and 8, 2019

#### PRC Confidential

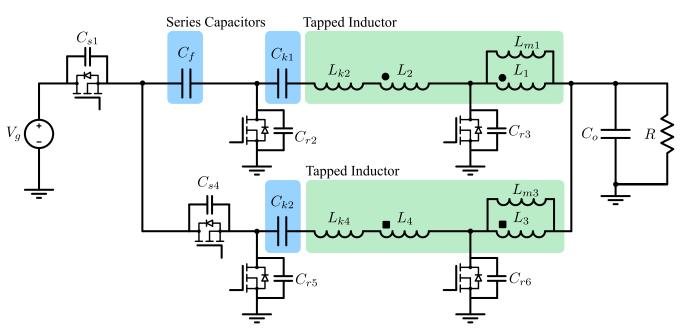

## Power Stage [1]

JRG<sup>®</sup> JUMP

- Inductances L<sub>k</sub> act as current source that can charge/discharge the output capacitance.

- The switch capacitor and tapped inductor extend the duty cycle.

- We have two more transistors that add gate charge losses and series resistance.

- Ck1 and Ck2 also adds series resistance.

[1] K. I. Hwu, et. Al., "An Expandable Two-Phase Interleaved Ultrahigh Step-Down Converter With Automatic Current Balance," 2017

10

New

Work

Georgia Tech

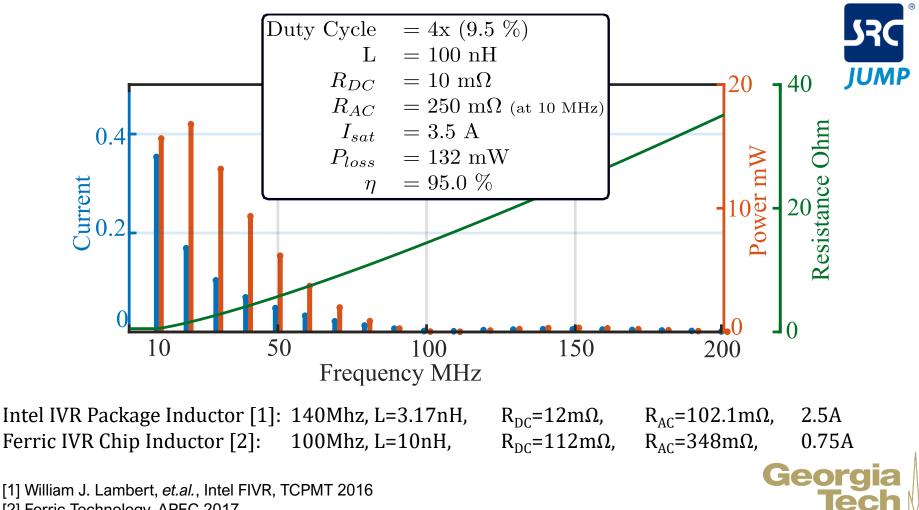

## **Challenges** – Inductor

The previous analysis allows us to determine the minimum inductor parameters to achieve 95% of inductor efficiency

[2] Ferric Technology, APEC 2017

**Inductor and Power Stage Co-Design**

**PRC Confidential**

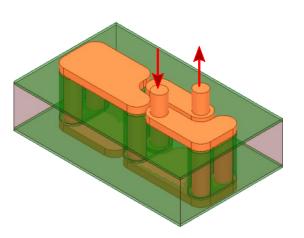

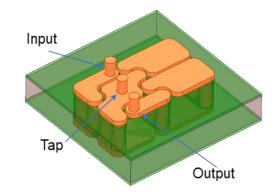

# **Proposed Inductor**

### New Work Packaging Research Center

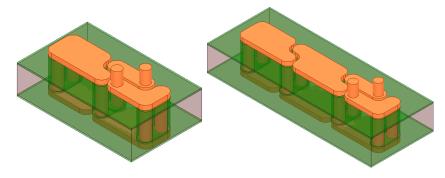

## To enable next generation IVR, we need an inductor than can

- Match the power stage duty cycle

- Be used as single inductor

- Be used as coupled or tapped inductor

- Be embedded in the package substrate

- Be compatible with multi-phase converters

- Have ultra-low losses

- Have high inductance density

- Have close magnetic path

November 7 and 8, 2019

### **PRC** Confidential

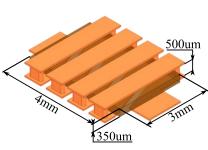

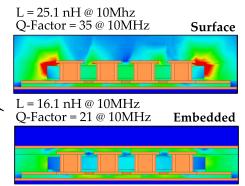

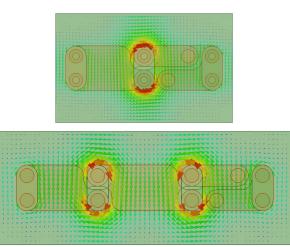

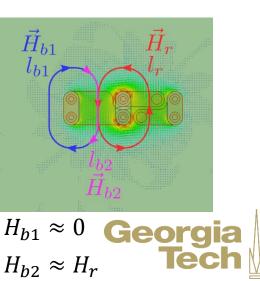

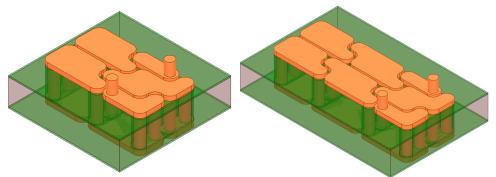

## **Proposed Inductor Structure**

Open magnetic loop inductors can lose more than 35% of inductance when are embedded [5]

Closed magnetic inductors are almost not affected by near conduction planes [5]

Invention Disclosure GTRC ID#8341

submitted on 11/05/2019

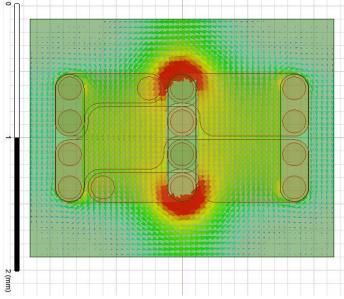

A via is the simplest structure that has a close magnetic path.

The inductor cell present a toroidal field distribution.

It also has an enclose field distribution, confined to the cell.

[5] Claudio Alvarez, *et.al.*, "Open and Closed Loop Inductors for High-Efficiency System-on-Package Integrated Voltage Regulators", ECTC 2019

### **Proposed Inductor Structure**

Invention Disclosure GTRC ID#8341 submitted on 11/05/2019

#### **PRC Confidential**

New

Work

### Increase the self inductance

Increase both the self and mutual inductance

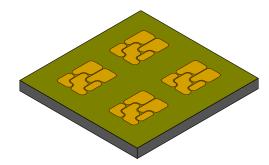

Several inductors can be built on the same magnetic sheet substrate.

Tap inductors can be easily obtained with coupling ratio greater than 0.90

Georgia

### PRC Confidential

### **Proposed Inductor Structure**

Invention Disclosure GTRC ID#8341 submitted on 11/05/2019

JRC

JUMP

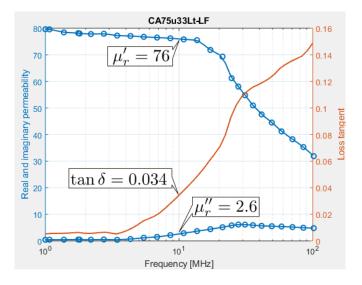

### **Required Magnetic Material**

| I <sub>DC</sub> [A]                    | 2.5 |

|----------------------------------------|-----|

| L [nH]                                 | 117 |

| L <sub>den</sub> [nH/mm <sup>3</sup> ] | 53  |

| $R_{DC} [m\Omega]$                     | 9.3 |

| $R_{AC} [m\Omega]$                     | 297 |

1.8 x 2.3 x 0.5 mm

| Duty cycle [%]          | 9.5  |

|-------------------------|------|

| Output power [mW]       | 2500 |

| DC Losses [mW]          | 58.1 |

| AC Losses [mW]          | 39.3 |

| Inductor Efficiency [%] | 96%  |

#### **PRC Confidential**

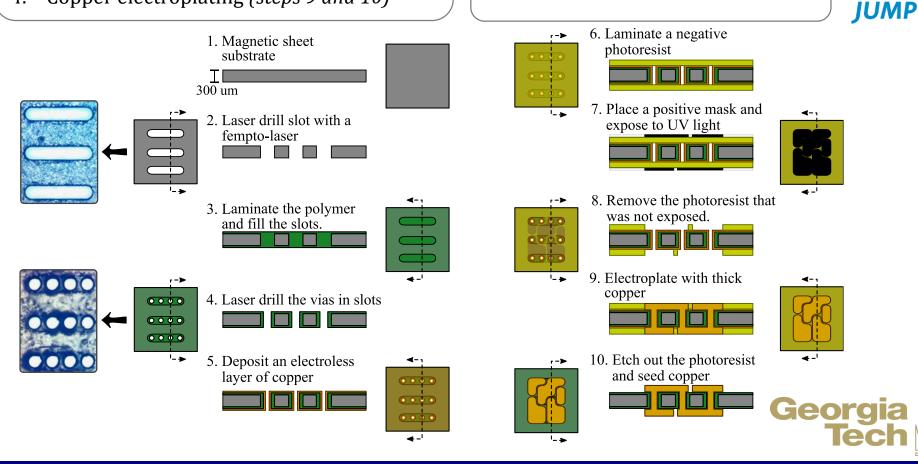

# **Fabrication Process**

New Work

The entire process is handled in

the Packaging Research Center

(PRC) at Georgia Tech.

### The process is divided in four major steps

- 1. Mechanical laser drilling (steps 1 to 4)

- 2. Electroless seed copper layer (*step 5*)

- 3. Lithography (steps 6 to 8)

- 4. Copper electroplating (steps 9 and 10)

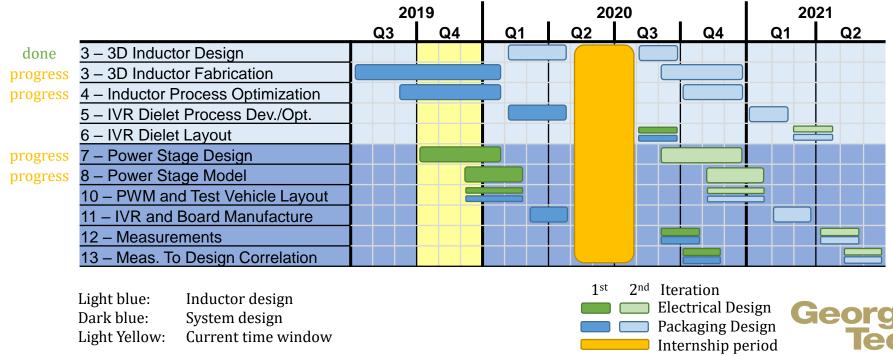

## Schedule

- Toroidal single inductor is already designed

- Fabrication is in process of optimization

- A single inductor based 4-phases buck is in design step

- A Journal paper will be prepared with the analysis results so far

- Next step will be preparing a measurement setup to measure the inductor under DC current bias and with triangular current waveform.

- Next iteration will be the design of a tapped inductor based converter

JUMP

**PRC Confidential**

# end.

# Thanks.