### PRC IAB Meeting

## Package-Integrated, Low-ESR, High-Density Capacitors for IVR

### Faculty:

- Dr. Himani Sharma

- Prof. M. Swaminathan

### Industry: Panasonic

- Senshu Takahiro

- Cheng Ping Lin

- Naoki Watanabe

### Students:

- Grant Spurney

- Mercy Daniel-Aguebor

## Outline

- □ Goals & Objectives

- Prior Work

- Technical Approach

- Results & Key Accomplishments

- **Comparison with Prior Art**

- □ Schedule

- □ Summary

## **Goals and Objectives**

• Demonstrate thin-film tantalum capacitors on silicon with >0.1  $\mu$ F/mm<sup>2</sup> for 3 V and >20 nF/mm<sup>2</sup> for 48V applications at 10 MHz switching and high current handling

• Specific Objectives & Targets:

| Parameter                                                |      | Objective                                                            | Challenges                                                                                          | Tasks                                                                                                |  |

|----------------------------------------------------------|------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| Capacitance Density<br>at 10 MHz and 100<br>µm thickness | 5 V  | >0.1 μF/mm²                                                          | Retain high volumetric                                                                              | Substrate-compatible<br>fabrication using high-<br>surface area, printed Ta                          |  |

|                                                          | 48 V | >20 nF/mm <sup>2</sup>                                               | density and low ESR for<br>high current handling with                                               |                                                                                                      |  |

| ESR and Frequency Stability                              |      | 1-10 MHz<br>ESR <50 milliohm                                         | small form-factor                                                                                   | nanoelectrodes                                                                                       |  |

| 3D Package Integration                                   |      | <ul> <li>~100 μm<br/>interconnects</li> <li>0% added area</li> </ul> | Capacitor compatibility<br>with via formation and<br>build-up processes                             | Integration directly on<br>silicon using scalable foil<br>transfer                                   |  |

| Reliability at High Operating<br>Temperature             |      | 125 °C                                                               | Conducting polymers are<br>susceptible to thermally<br>induced moisture<br>absorption and oxidation | Develop barrier-material<br>strategy to limit moisture<br>infiltration and pass<br>reliability tests |  |

# **Prior Art**

|                    | Murata Thin MLCC            | IPDiA Silicon Trench | AVX Ta Chip | <u>GT Ta Thin-film</u> |

|--------------------|-----------------------------|----------------------|-------------|------------------------|

| Volumetric Density | 5 μF/mm³                    | 2 μF/mm³             | 10 μF/mm³   | >10 μF/mm³             |

| Thickness          | 100 μm                      | 100 µm               | 600 μm      | 100 µm                 |

| Freq. Stability    | 10-50 MHz                   | >100 MHz             | 300 kHz     | 1-10 MHz               |

| ESR                | ~15-50 mΩ                   | 200 mΩ               | 500 mΩ      | ~50 mΩ                 |

| % ΔC/V             | -13 % to -70%<br>(1 to 4 V) | ~ 0 %                | ~ 0 %       | ~ 0 %                  |

| Max. Temp          | 85° C                       | 150° C               | 105° C      | 125° C                 |

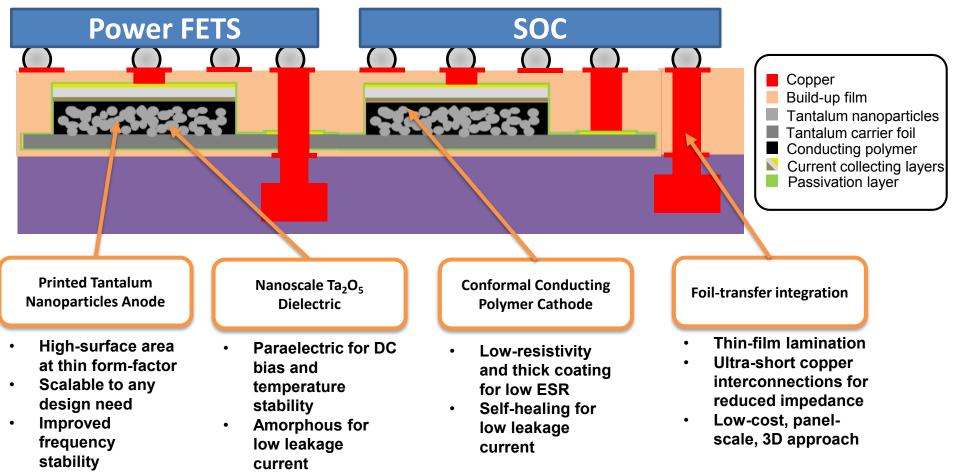

# **Technical Approach**

# **Research Tasks**

### **PRC** Confidential

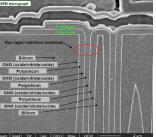

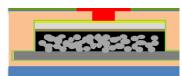

#### **Task 2: Capacitor Task 1: Capacitor Fabrication &** Design Integration Design electrode microstructure for high-**Develop process for capacitor** density, improved impedance materials formation characteristics, and frequency stability Sintered and anodized Ta-Ta capacitor equivalent $Ta_2O_5$ Ta Wire nanoparticles circuit Ta Particles $Ta_2O_5$ Demonstrate performance of embedded capacitors meeting design objectives PEDOT Ta<sub>2</sub>O<sub>5</sub> Simplified Fmbedded FFM model Ta thinof capacitor nanoparticle film capacitor 100 nm 15.0kV 5.8mm x250 BSECOM

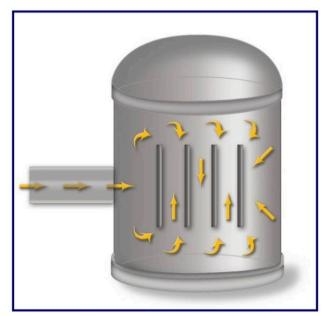

Task 3: Capacitor Reliability Evaluation

Develop material system strategy to limit diffusion of moisture into capacitor structure at high temperatures

Moisture absorption in PEDOT:PSS cathode material

Demonstrate reliability of the capacitors using accelerated stress testing

HAST chamber

### Georgia Institute of Technology

### Nov. 7-8, 2019

## **Prior Work**

### □ Capacitors fabricated and tested meeting designs objectives:

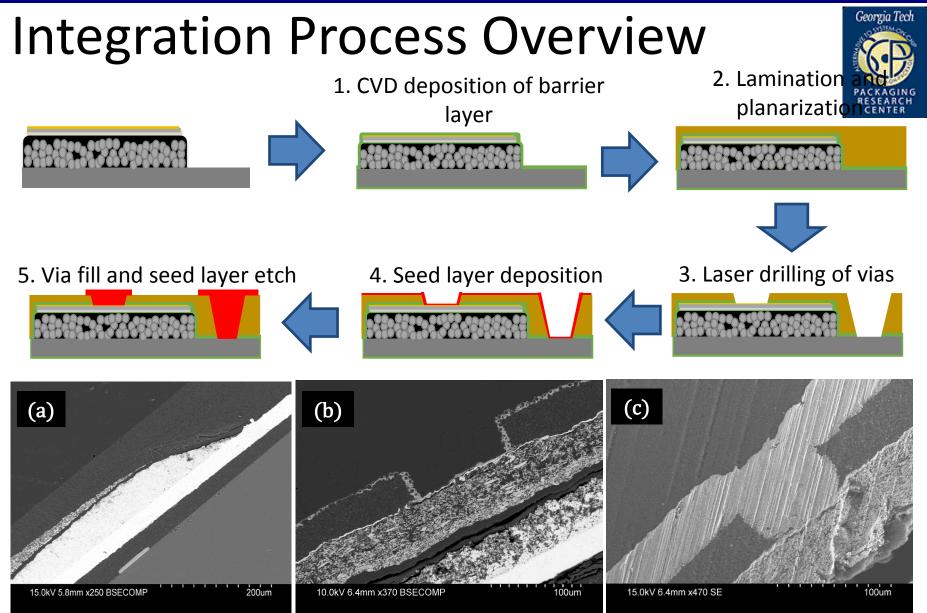

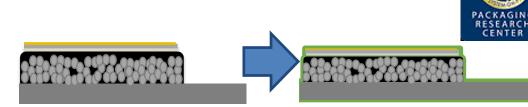

Foil-transfer lamination process optimized for successful capacitor integration on organic, silicon, or glass substrate

Preliminary reliability testing results showed use of thin-film diffusion barriers improve high-temperature lifetime of capacitors

### **PRC** Confidential

(a) Thin-film Ta capacitor laminated and planarized on silicon (b) Thin-film capacitor after laser drilling of via and electroless copper deposition (c) Partially filled copper via contacting Au/silver paste cathode layers

### **PRC** Confidential

Georgia Tech

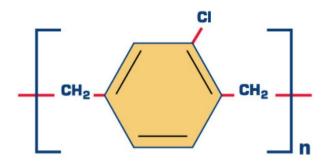

Barrier Layer Deposition of Parylene C using CVD

*Linear structure & aromatically stabilized Cl in Parylene C structure*  $\rightarrow$  *High crystallinity*

Low-temperature CVD of Parylene → Good conformality and strong adhesion

2 µm of Parylene C deposited on all samples

Previously showed thicker Parylene layer can be used to increase number of capacitors passing 85° C/85% relative humidity/3.3 V bias HAST for 335 hours

| Parylene C<br>Thickness | 500 nm | 700 nm | 1000 nm |

|-------------------------|--------|--------|---------|

| Total Passing<br>Rate   | 14 %   | 57 %   | 75 %    |

Georgia Institute of Technology

### **PRC** Confidential

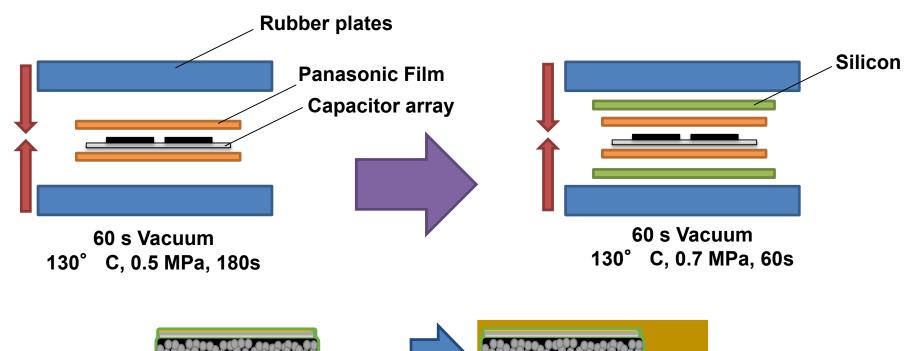

# Lamination with Panasonic Film

# Laser Drilling of Vias using UV Laser

### Drilling conditions:

| Film:                   |         | XV2106FG | XV2105FG | XV2103FG |

|-------------------------|---------|----------|----------|----------|

| Power                   | Anode   | 12 W     | 5 W      | 4.5 W    |

|                         | Cathode | 5 W      | 5 W      | 4 W      |

| Repetitions             | Anode   | 100      | 100      | 100      |

|                         | Cathode | 100      | 100      | 100      |

| Via Opening<br>Diameter | Anode   | 155 μm   | 155 μm   | 155 μm   |

|                         | Cathode | 155 μm   | 155 μm   | 155 μm   |

• Followed by 12 min desmear in Permanganate etch to remove leftover polymer debris

### PRC Confidential

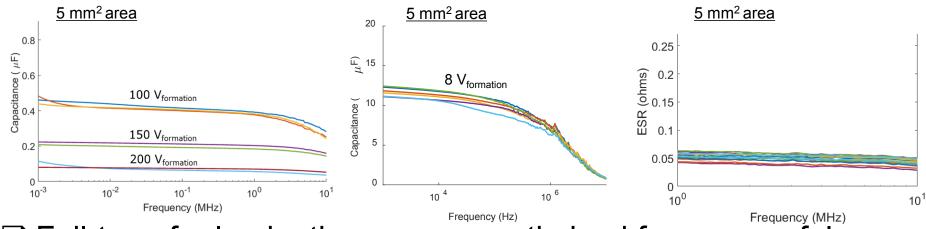

# Electrical Characterization of Integrated Capacito

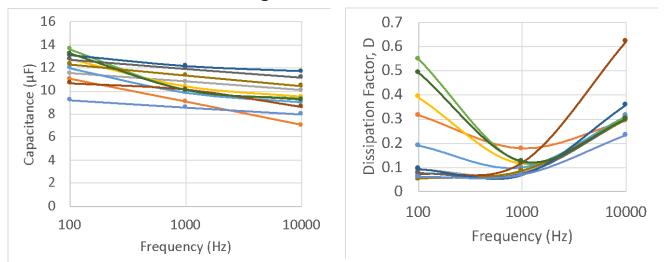

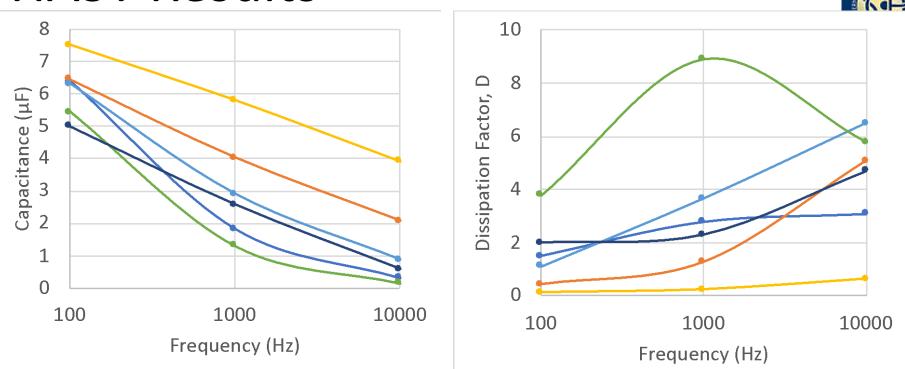

• Measurements of capacitors embedded in XV2103FG film

• Measurements of capacitors embedded in XV2105FG film

### **PRC** Confidential

Georgia Tech

# **HAST Results**

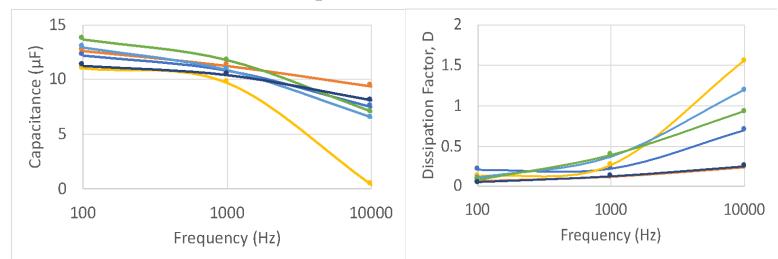

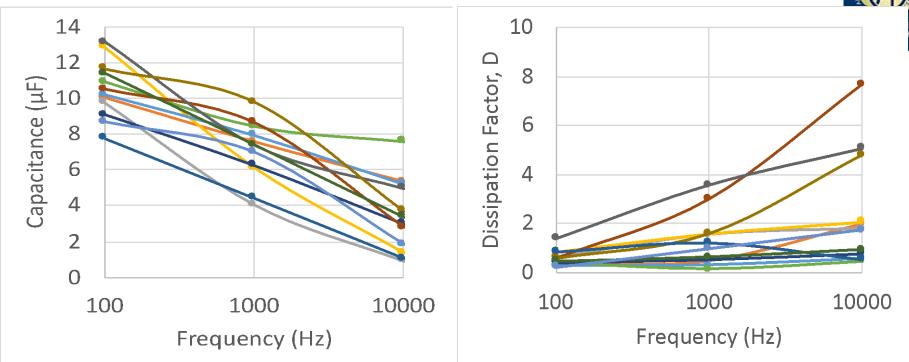

• Measurements of capacitors embedded in XV2105FG film

Average capacitance (1 kHz): 4.07  $\mu$ F  $\rightarrow$  (-63.8 %) Average Dissipation Factor (100 Hz): 1.38  $\rightarrow$  (+228%) Average ESR (100 kHz): 8.42  $\Omega \rightarrow$  (x 5.32)

### **PRC** Confidential

Georgia Tech

# HAST Results

• Measurements of capacitors embedded in XV2103FG film

Average capacitance (1 kHz): 10.27  $\mu$ F  $\rightarrow$  (-3.85 %) Average Dissipation Factor (100 Hz): 0.934  $\rightarrow$  (+93.4 %) Average ESR (100 kHz): 13.91  $\Omega \rightarrow$  (x 26.2)

## Summary

- Capacitors successfully passed 85/85 HAST for 335 hours

- Some capacitors show ability to pass 125/85 HAST for 96 hours

- Least amount of degradation observed using XV2103FG film

- XV2103FG film showed the most promising results

- Very little decrease in capacitance and increase in dissipation factor

- Thinner form factor

- ESR increased dramatically in most cases, but unclear how much of this can be attributed to the increase in resistance coming from the solder versus the capacitors themselves

- Next phase of project will focus on capacitor integration with magnetic substrate to provide on-package LC power conversion network