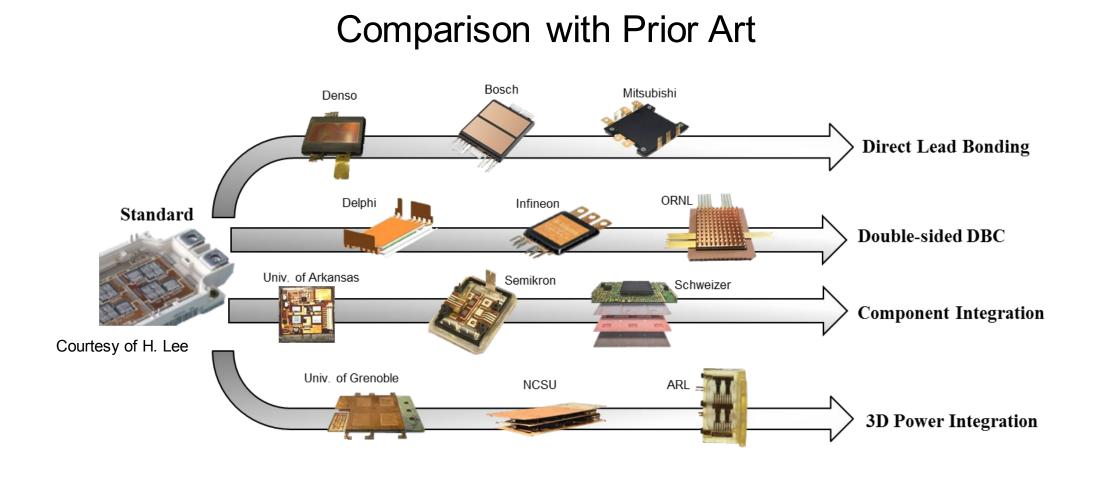

# **SiC-Based Power Electronics for EV Drive: Introduction**

Faculties: Dr. Vanessa Smet Prof. Antonia Antoniou Prof. C.P. Wong Prof. Yogendra Joshi Prof. Madhavan Swaminathan Prof. Deepak Divan, Prasad Kandula (Center for Distributed Energy) Students: Haksun Lee Michael Mauger Kashyap Mohan Jiaxiong Li Justin Broughton Ryan Wong Hakki Torun

Industry Collaborators: Bosch, Toyota

# Outline

□ Background & Technical Challenges

Objectives

Technical Approach

□ Prior Work

- Results & Key Accomplishments

- Comparison with Prior Art

# □ Summary

**PRC** Confidential

# **Background & Technical Challenges**

### **PRC** Confidential

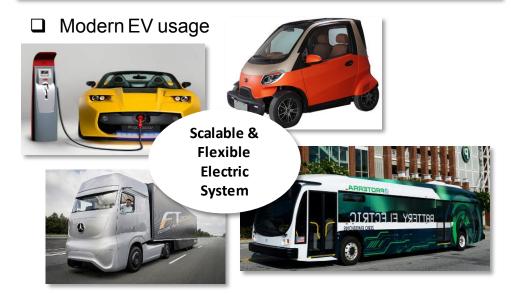

#### Key Application: Electric Vehicles

### **D** Trend to increase integration density: in-wheel

Source: Protean (~50kW/0.5L)

→ Transition to SiC devices is key to reaching required power densities (2X)

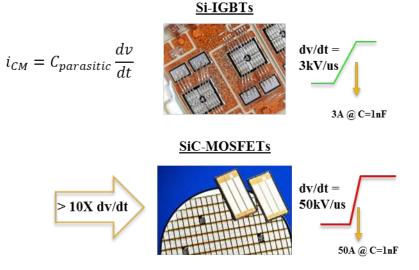

### Challenges with SiC: Why Packaging is More Critical

- □ Increased switching speeds: aggravated effect of package parasitics

- Parasitic L: increased di/dt with SiC

- Parasitic C: increased dv/dt and common mode noise

- Shrinking of die size and increased power ratings: increased thermal density

- Hot spot mitigation

- > Transient thermal performance more critical

- While SiC devices can sustain higher T<sub>jmax</sub>, the package will be exposed to increased operating temperatures as well → reliability?

- $\rightarrow$  Packaging is today the limiting factor in realizing the promises of SiC

## **PRC** Confidential

# Objectives

# Develop and demonstrate advanced packaging solutions for SiC-based power electronics with:

- > Modular design: flexibility in power level

- > Miniaturization: module size ~25% vs. Si  $\rightarrow$  100kW/0.5L for in-wheel inverters

- ✓ High-frequency switching

- ✓ Increased functional density with heterogeneous integration (e.g. cooling)

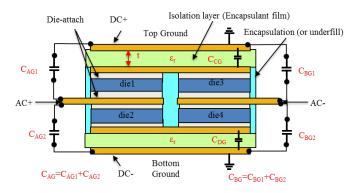

- > Minimized package parasitics (L<5nH,  $C_{AG}$ ,  $C_{BG}$ <0.1pF), increased dv/dt capability  $\rightarrow$  wirebond-less

- > High operating temperatures (junction and coolant?) and improved thermal behavior

- > Fundamental understanding of multiphysics trade-offs

| Parameters                | Current Packaging Solutions  | Our Targets                   |

|---------------------------|------------------------------|-------------------------------|

| Breakdown Voltage         | 10kV                         | >30kV                         |

| Heat Flux                 | 200W/cm <sup>2</sup>         | 1kW/cm <sup>2</sup>           |

| Max. Junction Temperature | 150-175°C                    | 250°C                         |

| Thermal Performance       | No thermal transient control | Thermal transient suppression |

| Reliability               | Poor at full device rating   | Improved                      |

### **PRC** Confidential

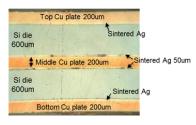

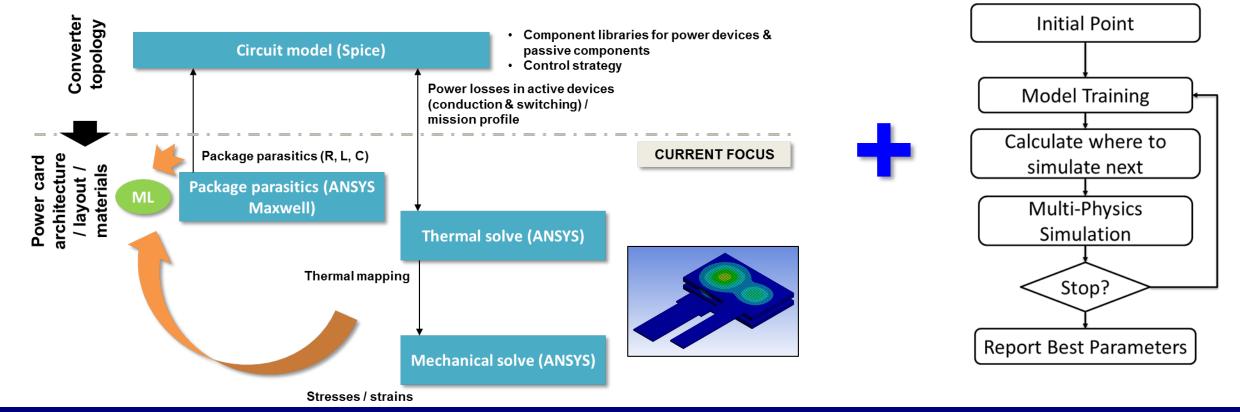

#### Georgia Tech **Technical Approach** ML-Assisted Design & Heterogeneous Functional Integration Machine learning (ML) based power module optimization (Bayesian active learning) **Circuit Topology 3D Stacked Power Multiphysics** Material **Cooling System** Modeling Innovations Cards Talk by H. Lee With Prof. Y. Joshi Poster by M. Mauger, P. Electrical, thermal, High-temperature, Kandula, D. Divan Die stacking Advanced cold plates mechanical HV mold compounds $\geq$ Non-Consortium (Prof. C.P. Wong) Manufacturing (2-phase) project (ARPA-E) Sintered Cu die- $\triangleright$ Testing Integrated cooling Soft switching attach (with Prof. A (new project, with (current switch) Antoniou) Prof. A. Antoniou) Low-CTE composite conductors (with Prof. Concept: die stacking Advanced cold plate with Sintered A. Antoniou) die attach additively manufactured foam From concept to realization: -Lead-frames Decoupled NP-Cu die-attach functional bridge rectifier SiC device Cu-Zn film Cu foil ~25µm Engineered resin Cu-Zn film & fillers High thermal conductivity thin-10 µm film insulator Georgia Institute of Technology Nov. 7-8, 2019

5

# Prior Work: May IAB Recap

#### **Material Developments**

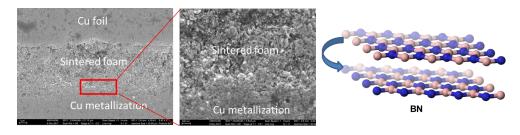

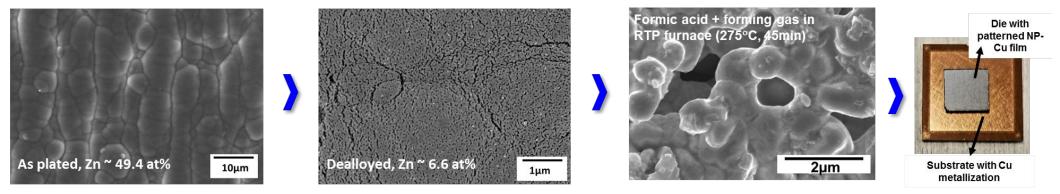

- NP-Cu die-attach insert with compliant Cu foil core (with Prof. A Antoniou)

- Resin / fillers formulation for high-temp. stability

& high thermal conductivity (Prof. C.P. Wong)

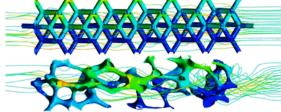

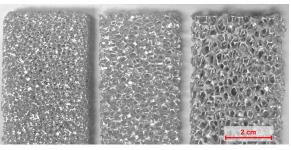

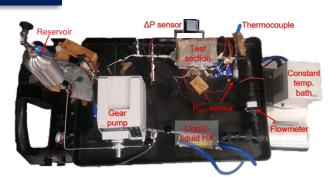

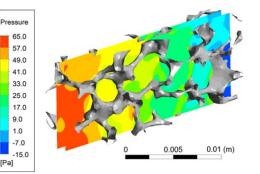

#### **Advanced Cold Plates**

Prof. Y. Joshi

- □ Flow loop setup complete

- Stochastic pore-scale model in agreement with experimental results: additively manufactured foams perform best

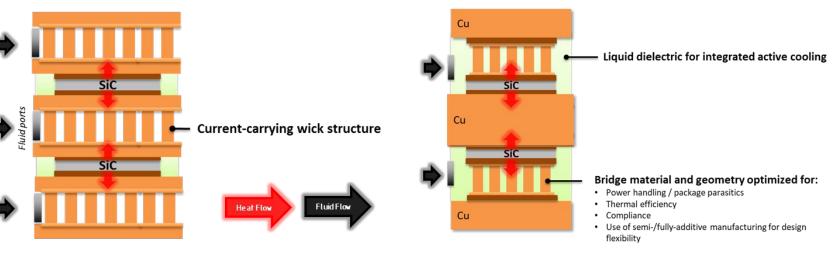

### **3D Stacked Power Module**

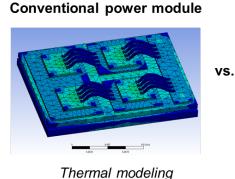

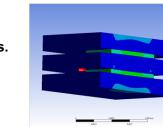

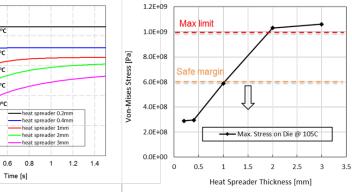

- Thermal modeling: ~5X reduction in junction-to-case Rth vs. conventional module

- □ Trade-off in Cu thickness for stress management: 200µm

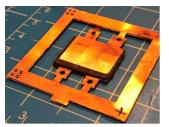

- □ Unit fabrication process steps established

62.3°C

56.4°C

50.7%

14.9°C

3D stacked power module

Stress analysis

### \_\_\_\_\_

#### Mechanical process demonstrator

**PRC** Confidential

350

340 도

330

320

300

0 0.2 0.4

# Results & Key Accomplishments: Material Innovations

#### **NP-Cu Die-Attach**

**PRC** Confidential

- Collaboration with Prof. A. Antoniou, On Semiconductor, poster by K. Mohan

- Lentified promising precursor alloy composition and dealloying parameters for SAP process manufacturability

- □ High densification confirmed (in formic acid)

- Expected to reach shear strength values of 40-50MPa

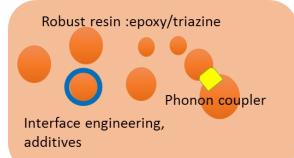

#### Mold Compounds

- Demonstration of high Tg cyanate ester/ epoxy (CE/EP) copolymer (>250°C)

- Progress in synthesis of BN-coated SiO<sub>2</sub> for high thermal epoxy composite

- Progress in formulation of resin systems for high BDV

#### Prof. C.P. Wong, poster by J. Li

#### High Thermal BN/SiO2 Hybrid Filler

Georgia Institute of Technology

# Results & Key Accomplishments: Power Module Integration & Cooling

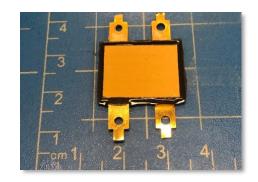

#### **3D Stacked Power Module**

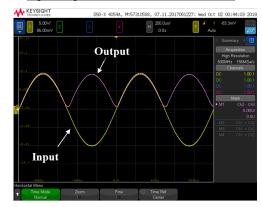

- Electrical simulation & measurements: significant improvements in package parasitics

- □ Full bridge rectifier with 200V/15A Si diodes fabricated and tested

### Talk & poster by H. Lee

I-V characteristic curve of diode

1.5

1.2

---bare die

-packaged die

0.9

0.6

0.3

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

-2.0

0.0

0.0

0.0

0.0

0.0

0.0

#### Input/output waveforms of FBR module

Resistive load (78  $k\Omega)$  at the output of rectifier

#### **Advanced Cold Plates**

- Dual computationalexperimental approach

- Performance comparison between traditional vs. AM foams

#### Prof. Y. Joshi, poster by J. Broughton

Georgia Institute of Technology

#### Nov. 7-8, 2019

CENTER

8

Advanced Cold Plates as Current Terminals

## **PRC** Confidential

# Increasing Functional & Power Density: Integrated Cooling

In collaboration with Prof. Y. Joshi & Prof. A. Antoniou, Bosch Poster by R. Wong

- Key concept: bring cooling closer to the heat sources (devices, high current terminals)

- □ Create hybrid electrical / thermal structures

- Multiphysics, multiscale modeling

- Machine-learning assisted design optimization

- Material innovations: use 3D interconnected Graphene (GP) foams to create low-CTE / highconductivity Cu-GP composites

# Plasma surface modification E-deposit Cu Molten Cu dir GP/Cu composite

GP on macro/nano Ni/Cu foam

GP foam

**Direct Chip Cooling with Liquid Dielectric**

### **PRC** Confidential

# Shaping the Landscape of Future WBG-Based Power Electronics

- □ Combine machine / active learning and multiphysics analysis to optimize, and ultimately generate new, **non-intuitive** SiC-based inverter package architectures

- □ Build and characterize prototypes based on ML-assisted design

Multiphysics Modeling Environment

In collaboration with Prof. M. Swaminathan, Toyota Talk & poster by H. Torun & R. Wong

# **Bayesian Active Learning**

#### Georgia Institute of Technology

### **PRC** Confidential

□ Combined benefits from 3D integration, heterogeneous integration & functional integration

- □ Focus on manufacturability & compatibility with industry-standard processes

- □ Inclusion of machine learning for multi-objective power module optimization

- □ Unique potential to go from co-design to prototyping and testing with focused GT team

# Summary

□ Research program is growing with an ecosystem of expert faculties coming together

- Addressing the transition to SiC from many angles to identify key integration strategies and package architectures, particularly for EVs

- Work is ongoing in parallel with Prof. S.C. Shen on vertical GaN devices (goal is to develop a GaN IGBT) as next roadmap

- Aiming at growing our prototyping and testing capability with more supply chain involvement